Editor’s take: Usually talking we’re massive followers of RISC V. It does some issues very nicely, handles many others nicely sufficient, and has clear indicators of adoption and enchantment. It meets an actual market want in an progressive method, precisely what we wish to see from our know-how. So we are saying this from a place of affection – RISC V goes to have a giant software program downside. The excellent news is that it might not matter.

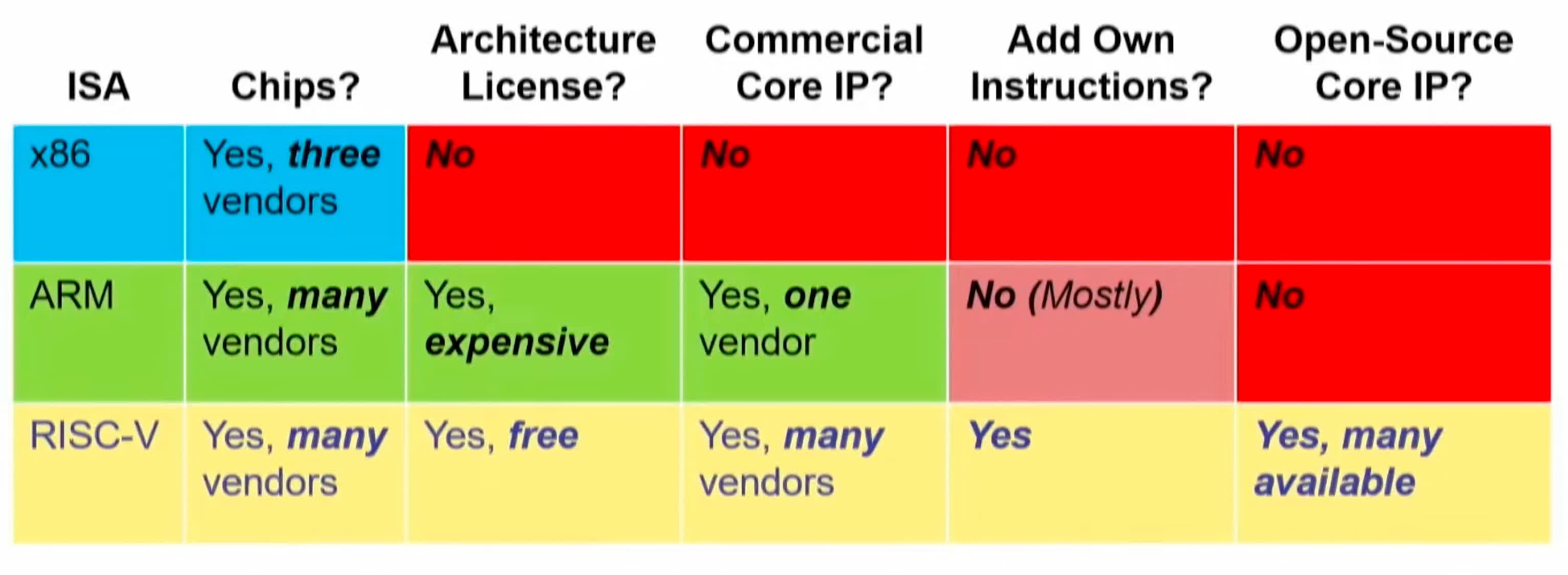

First, some background. RISC V is an open-source instruction set architecture (ISA), a “free” different to Arm. ISAs present a set of widespread, necessary however unglamorous “blueprints” for processors. Each processor wants what an ISA offers to do some primary math. They take loads of work to design and keep however don’t present a lot end-product differentiation, which implies that the chip firms who use them see nice benefit in outsourcing this work to a 3rd get together like Arm.

The entire level of processors is to run some type of software program. And despite the fact that the ISA and the software program developer are a number of layers aside, ISAs are so basic to chips that modifications in an ISA create actual software program issues.

Strive downloading some widespread programming language on a brand new Apple M1-powered MacBook and you might be more likely to discover that the software program doesn’t work on the M1 or requires some different beta model. That is really pretty necessary as a result of it implies that anybody operating legacy code has to endure important friction to change to a brand new ISA.

ISAs are extremely sticky, altering to a brand new one is one thing that almost all chip firms detest to do. As an example, Qualcomm has been constructing Arm-based chips for many years, and despite the fact that Arm is suing them, it’s unlikely that Qualcomm would ever transfer its core merchandise to RISC V as a result of it will render all of the software program written for Qualcomm-based chips unwieldy, if not unworkable. We don’t wish to overstate this, switching isn’t not possible, it’s simply exhausting. As we stated above, it’s loads of friction.

Supply: Cadence

This might have been a giant downside for RISC V to realize adoption. Nonetheless, it entered the market at an virtually excellent second. Simply as Arm went into hibernation within the coddling arms of Softbank and misplaced its motivation to draw new prospects, semis startups started sprouting once more for the primary time in a decade. That features budding development of US semis startups and an absolute explosion of them in China. None of these firms had many years of legacy Arm dependencies and have been completely happy to go together with the answer that price nothing.

However there may be one downside with all of this. RISC V is open-source, which implies that anybody who needs to design a RISC V chip largely has the flexibleness to make all types of modifications to their particular implementation of the ISA. That implies that everybody’s RISC V is a bit of totally different. The RISC V group foresaw this downside and laid down a set of compatibility necessities, and whereas everybody needs to abide by these, there isn’t a actual enforcement mechanism to stop it from occurring.

Because of this implementation from main standalone RISC V chip designers like SiFive, Andes and CodaSIP might all be barely totally different. Everybody complies fully with all the principles, however some individuals comply extra fully. And throughout the many massive chip firms with RISC V designs, who is aware of what’s going on.

This in all probability implies that software program written for one RISC V chip is not going to run on one other RISC V chip, or a minimum of no run nicely.

As soon as upon a time that will have been a present stopper. The 1980’s noticed a complete conflict of working techniques whose end result depended very closely on the underlying chips and ISAs. This sort of software program downside would have severely hobbled the enchantment of RISC V, particularly for a number of the extra bold initiatives on the market like CPUs for servers. However this time will likely be totally different. There are actually two the explanation why this RISC V software program fragmentation might not find yourself mattering that a lot.

First, the best way we use software program has modified. Working techniques matter lower than they used to due to the Web and cloud computing (they nonetheless matter however not in the identical approach.) As long as that underlying processor can deal with primary internet visitors, there will likely be a solution to run software program on it. There’ll possible be issues porting many widespread software program functions to RISC V, and as now we have famous typically, that is the issue that stored Arm out of the information middle, however that’s solely a small a part of the market.

The second purpose why this may occasionally not matter a lot is that a lot of what RISC V is getting used for doesn’t depend on widespread software program – there are tons of of RISC V chips being designed for IoT, industrial and different embedded functions. We predict RISC V will come to dominate this market. Until somebody comes up with an working system for the Web of Issues (IoT), there actually isn’t any want for a typical chip structure for these gadgets. And we’re agency believers that there will never be an working system for IoT.

It is also totally doable that sometime RISC V’s software program atmosphere will converge on extra appropriate options. This can take years and be stuffed with types of issues — anybody keep in mind printer and GPU driver incompatibility? — however it’s nonetheless possible.

At this stage, RISC V seems unstoppable. That could be a good factor. However it isn’t a one-size-fits-all answer, and it’ll encounter its share of rising pains, and plenty of of these will happen in and round software program compatibility. This doesn’t current the identical barrier it as soon as did.

Source link